## DISTRIBUTED SYSTEMS: PARADIGMS AND MODELS Academic Year 2012–2013

M. Danelutto Version September 5, 2014

Teaching material - Laurea magistrale in Computer Science and Networking

## CONTENTS

| Pref<br>Ack | ace<br>nowled | 1<br>3    |                                               |     |

|-------------|---------------|-----------|-----------------------------------------------|-----|

| 1           |               | llel hard |                                               |     |

|             | (nee          | ds parall | lel software)                                 | 1   |

|             | 1.1           | Hardw     | vare for parallel/distributed computing       | 2   |

|             |               | 1.1.1     | Evolution of CPUs                             | 3   |

|             |               | 1.1.2     | High performance computing architectures      | 8   |

|             |               | 1.1.3     | Cloud                                         | 9   |

|             | 1.2           | Paralle   | el software urgencies                         | 11  |

| 2           | Para          | llel prog | ramming: introducing the concept              | 13  |

|             | 2.1           | Concu     | rrent activity graph                          | 16  |

|             | 2.2           | Coord     | ination                                       | 17  |

|             | 2.3           | Functi    | ional and non functional code                 | 18  |

|             | 2.4           | Perfor    | mance                                         | 19  |

|             | 2.5           | Other     | non functional concerns                       | 21  |

|             |               | 2.5.1     | Load balancing                                | 21  |

|             |               | 2.5.2     | Reliability                                   | 22  |

|             |               | 2.5.3     | Security                                      | 23  |

|             |               | 2.5.4     | Power management                              | 24  |

|             | 2.6           | "Class    | sical" parallel programming models            | 25  |

|             |               | 2.6.1     | POSIX/TCP                                     | 25  |

|             |               | 2.6.2     | Command line interface                        | 28  |

|             |               | 2.6.3     | MPI                                           | 28  |

|             | 2.7           | Impler    | menting parallel programs the "classical" way | 31  |

|             |               |           |                                               | iii |

|   |       | 2.7.1     | The application                                                  | 31  |

|---|-------|-----------|------------------------------------------------------------------|-----|

|   |       | 2.7.2     | The concurrent activity graph                                    | 31  |

|   |       | 2.7.3     | Coordination                                                     | 31  |

|   |       | 2.7.4     | Implementation                                                   | 31  |

|   |       | 2.7.5     | Code relative to the implementation handling termination but     |     |

|   |       |           | not handling worker faults                                       | 32  |

|   |       | 2.7.6     | Adding fault tolerance (partial)                                 | 40  |

| 3 | Algo  | rithmic s | skeletons                                                        | 49  |

|   | 3.1   | Algori    | thmic skeletons: definition(s)                                   | 50  |

|   |       | 3.1.1     | The skeleton advantage                                           | 52  |

|   |       | 3.1.2     | The skeleton weakness                                            | 54  |

|   | 3.2   | Skelete   | ons as higher order functions with associated parallel semantics | 54  |

|   |       | 3.2.1     | Stream modelling                                                 | 57  |

|   | 3.3   | A sim     | ple skeleton framework                                           | 58  |

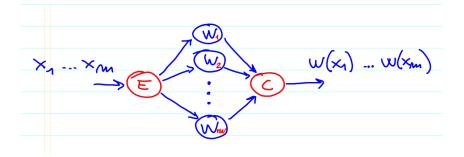

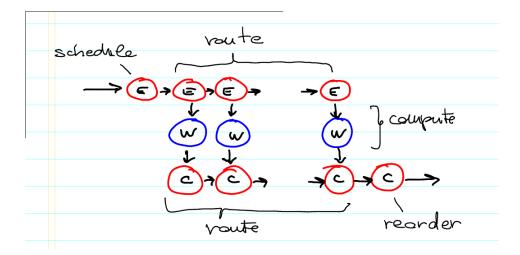

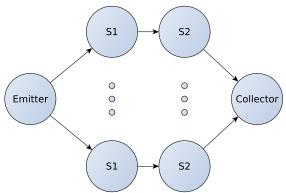

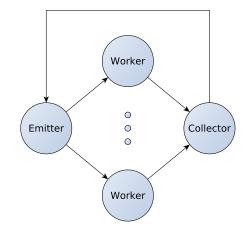

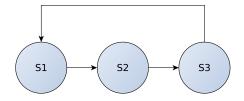

|   |       | 3.3.1     | Stream parallel skeletons                                        | 58  |

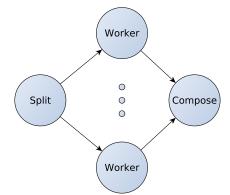

|   |       | 3.3.2     | Data parallel skeletons                                          | 59  |

|   |       | 3.3.3     | Control parallel skeletons                                       | 63  |

|   |       | 3.3.4     | A skeleton framework                                             | 64  |

|   |       | 3.3.5     | Skeleton programs                                                | 65  |

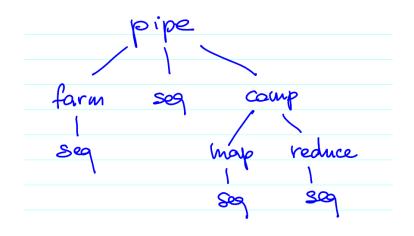

|   | 3.4   | Algori    | thmic skeleton nesting                                           | 66  |

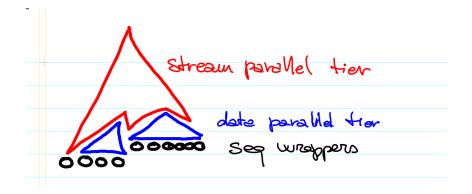

|   |       | 3.4.1     | Sequential code wrapping                                         | 67  |

|   |       | 3.4.2     | Full compositionality                                            | 69  |

|   |       | 3.4.3     | Two tier model                                                   | 69  |

|   | 3.5   | Statele   | ess vs. statefull skeletons                                      | 70  |

|   |       | 3.5.1     | Shared state: structuring accesses                               | 71  |

|   |       | 3.5.2     | Shared state: parameter modeling                                 | 73  |

| 4 | Impl  | ementat   | ion of algorithmic skeletons                                     | 77  |

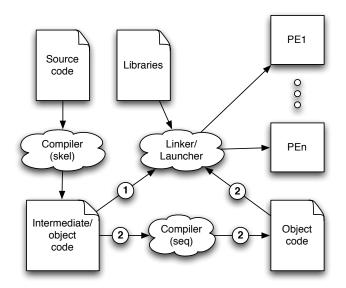

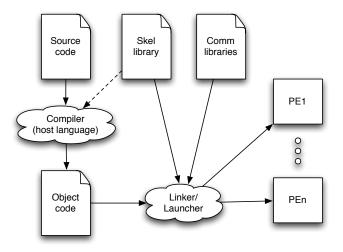

|   | 4.1   | Langu     | ages vs. libraries                                               | 77  |

|   |       | 4.1.1     | New language                                                     | 77  |

|   |       | 4.1.2     | Library                                                          | 78  |

|   | 4.2   |           | ate based vs. macro data flow implementation                     | 80  |

|   |       | 4.2.1     | Template based implementations                                   | 80  |

|   |       | 4.2.2     | Macro Data Flow based implementation                             | 86  |

|   |       | 4.2.3     | Templates vs. macro data flow                                    | 90  |

|   | 4.3   | Compo     | onent based skeleton frameworks                                  | 90  |

| 5 | Perf  | ormance   | models                                                           | 93  |

|   | 5.1   | Model     | ing performance                                                  | 94  |

|   | ~ • • | 5.1.1     | "Semantics" associated with performance measures                 | 95  |

|   | 5.2   | -         | ent kind of models                                               | 96  |

|   | 5.3   |           | ative approaches                                                 | 99  |

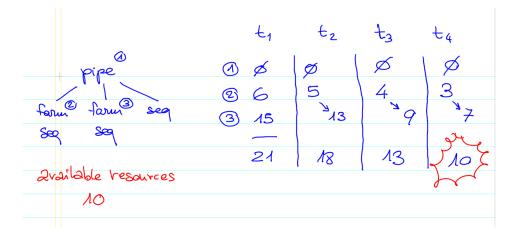

|   | 5.4   |           | performance models                                               | 100 |

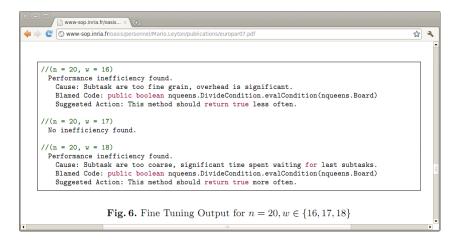

|   |       | 5.4.1     | Compile time usage                                               | 101 |

|   |       |           |                                                                  |     |

CONTENTS v

|   |       | 5.4.2                   | Run time usage                                                | 102 |

|---|-------|-------------------------|---------------------------------------------------------------|-----|

|   |       | 5.4.3                   | Post-run time usage                                           | 103 |

|   | 5.5   | Skeletc                 | on advantage                                                  | 104 |

|   | 5.6   |                         | oring application behaviour                                   | 105 |

|   | 5.7   | Perform                 | nance model design                                            | 107 |

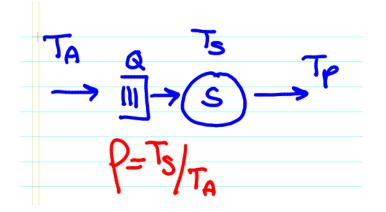

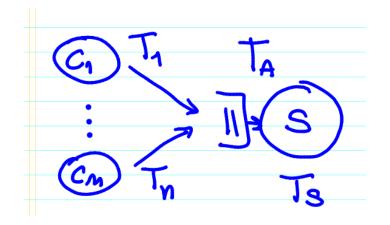

|   |       | 5.7.1                   | Analytical performance models                                 | 107 |

|   |       | 5.7.2                   | Queue theory                                                  | 108 |

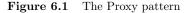

| 6 | Para  | llel desig              | n patterns                                                    | 113 |

|   | 6.1   | Design                  | patterns                                                      | 113 |

|   | 6.2   | Paralle                 | el design patterns                                            | 115 |

|   |       | 6.2.1                   | The parallel design pattern design spaces                     | 116 |

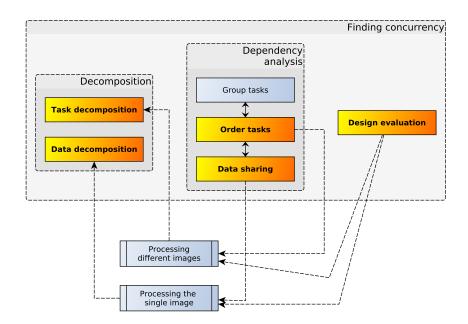

|   |       | 6.2.2                   | Finding concurrency design space                              | 117 |

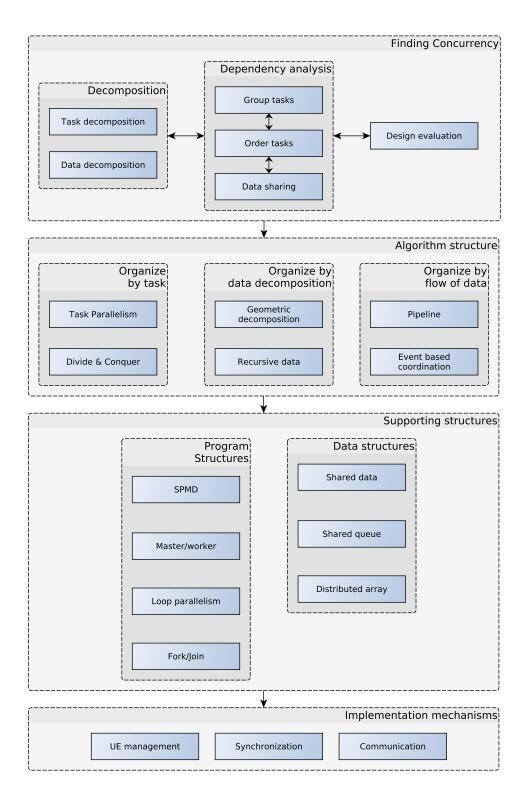

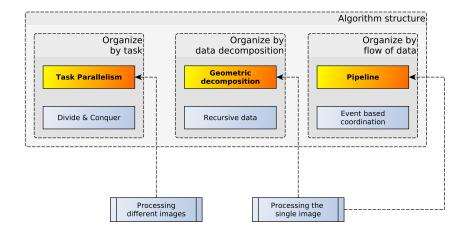

|   |       | 6.2.3                   | Algorithm structure design space                              | 119 |

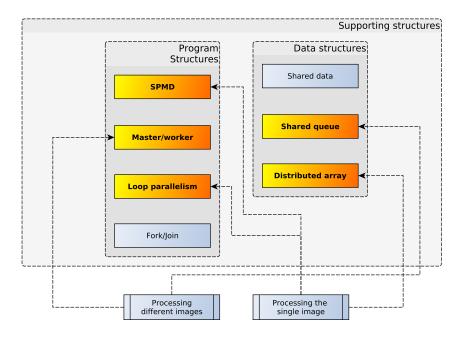

|   |       | 6.2.4                   | Supporting structure design space                             | 121 |

|   |       | 6.2.5                   | Implementation mechanisms design space                        | 124 |

|   | 6.3   | Sample                  | e parallel design pattern usage: image processing application |     |

|   |       | $\operatorname{design}$ |                                                               | 125 |

|   |       | 6.3.1                   | Application analysis                                          | 125 |

|   |       | 6.3.2                   | Exploring the "finding concurrency" design space              | 125 |

|   |       | 6.3.3                   | Exploring the "algorithm structure" design space              | 126 |

|   |       | 6.3.4                   | Exploring the "supporting structures" design space            | 128 |

|   |       | 6.3.5                   | Exploring the "implementation mechanisms" design space        | 129 |

|   | 6.4   | Compa                   | aring parallel design patterns and algorithmic skeletons      | 129 |

| 7 | Skele | eton desi               | gn                                                            | 133 |

|   | 7.1   | Cole m                  | anifesto principles                                           | 134 |

|   |       | 7.1.1                   | Summarizing                                                   | 136 |

|   | 7.2   | Lookin                  | g for (new) skeletons                                         | 136 |

|   |       | 7.2.1                   | Analysis                                                      | 136 |

|   |       | 7.2.2                   | Synthesis                                                     | 137 |

|   | 7.3   | Skeletc                 | ons vs templates                                              | 137 |

| 8 | Tem   | plate des               | sign                                                          | 139 |

|   | 8.1   | Templa                  | ate building blocks                                           | 141 |

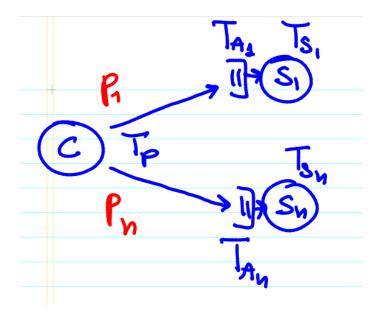

|   |       | 8.1.1                   | Client-server paradigm                                        | 143 |

|   |       | 8.1.2                   | Peer-to-peer resource discovery                               | 143 |

|   |       | 8.1.3                   | Termination                                                   | 144 |

|   | 8.2   | Cross-s                 | skeleton templates                                            | 145 |

|   | 8.3   |                         | e template mechanisms                                         | 146 |

|   |       | 8.3.1                   | Double/triple buffering                                       | 146 |

|   |       | 8.3.2                   | Time server                                                   | 147 |

|   |       | 8.3.3                   | Channel name server                                           | 148 |

|   |       | 8.3.4                   | Cache pre-fetching                                            | 149 |

|   |       | 8.3.5                   | Synchronization avoidance                                     | 151 |

|   |       |                         |                                                               |     |

\_\_\_\_\_

| VI CONTENTS |

|-------------|

|             |

|    | 8.4   | Sample   | e template design                                          | 153 |

|----|-------|----------|------------------------------------------------------------|-----|

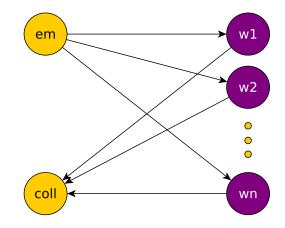

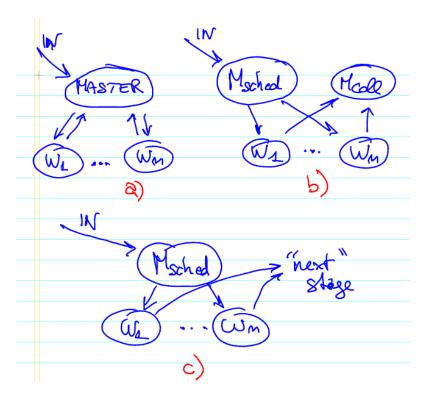

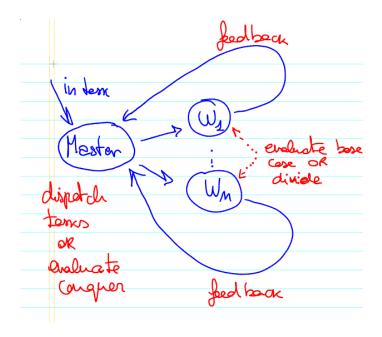

|    |       | 8.4.1    | Master worker template                                     | 153 |

|    |       | 8.4.2    | Farm with feedback                                         | 155 |

|    | 8.5   | Sequen   | tial code optimization                                     | 157 |

| 9  | Porta | bility   |                                                            | 163 |

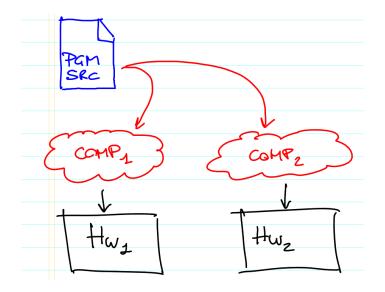

|    | 9.1   | Portab   | ility through re-compiling                                 | 165 |

|    |       | 9.1.1    | Functional portability                                     | 165 |

|    |       | 9.1.2    | Performance portability                                    | 166 |

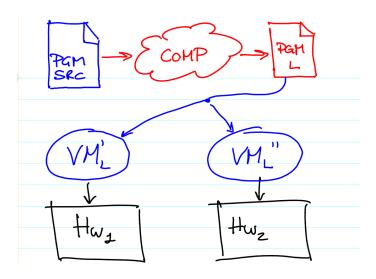

|    | 9.2   | Portab   | ility through virtual machines                             | 167 |

|    | 9.3   | Hetero   | geneous architecture targeting                             | 168 |

|    | 9.4   | Distrib  | uted vs multi-core architecture targeting                  | 170 |

|    |       | 9.4.1    | Template/MDF interpreter implementation                    | 171 |

|    |       | 9.4.2    | Communication & synchronization                            | 172 |

|    |       | 9.4.3    | Exploiting locality                                        | 172 |

|    |       | 9.4.4    | Optimizations                                              | 173 |

| 10 | Adva  | nced fea | itures                                                     | 177 |

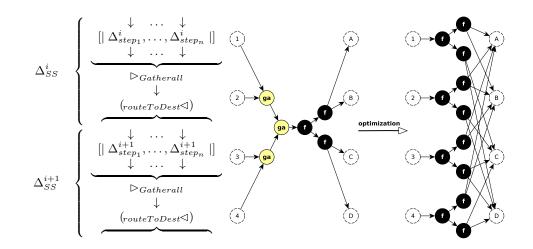

|    | 10.1  | Rewrit   | ing techniques                                             | 177 |

|    | 10.2  | Skeletc  | on rewriting rules                                         | 179 |

|    | 10.3  | Skeletc  | n normal form                                              | 180 |

|    |       | 10.3.1   | Model driven rewriting                                     | 182 |

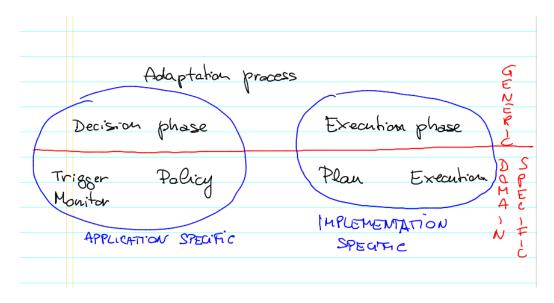

|    | 10.4  | Adapti   | vity                                                       | 183 |

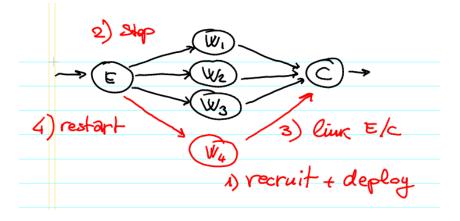

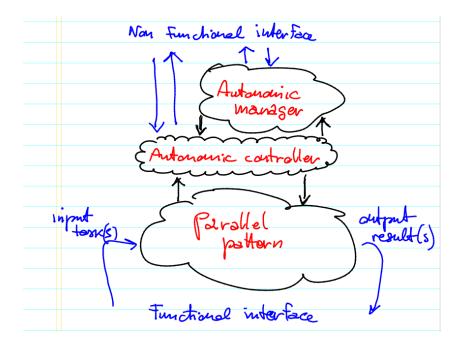

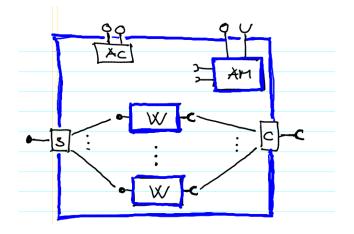

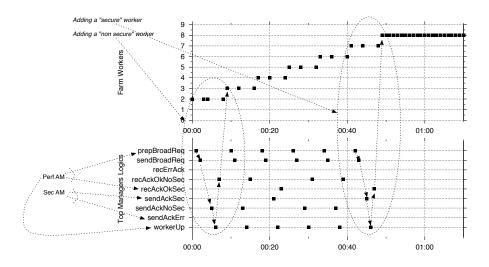

|    | 10.5  | Behavi   | oural skeletons                                            | 188 |

|    |       | 10.5.1   | Functional replication behavioural skeleton in GCM         | 191 |

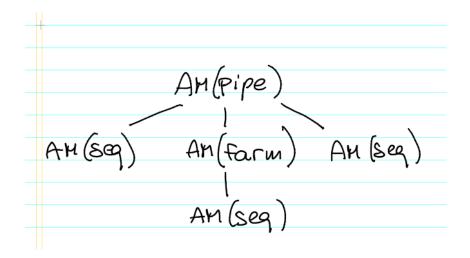

|    |       | 10.5.2   | Hierarchical management                                    | 193 |

|    |       | 10.5.3   | Multi concern management                                   | 198 |

|    |       | 10.5.4   | Mutual agreement protocol                                  | 201 |

|    |       | 10.5.5   | Alternative multi concern management                       | 204 |

|    | 10.6  | Skeletc  | on framework extendibility                                 | 206 |

|    |       | 10.6.1   | Skeleton set extension in template based frameworks        | 207 |

|    |       | 10.6.2   | Skeleton set extension through intermediate implementation |     |

|    |       |          | layer access                                               | 207 |

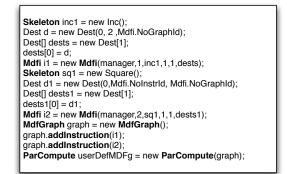

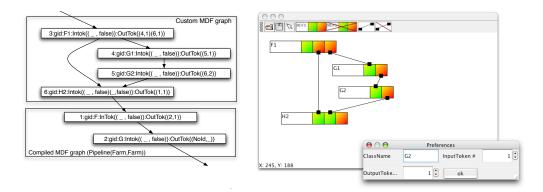

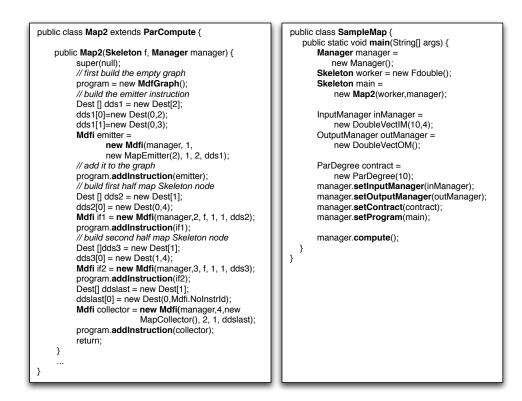

|    |       | 10.6.3   | User-defined skeletons in muskel                           | 208 |

| 11 | Struc | tured sk | eleton/pattern design                                      | 213 |

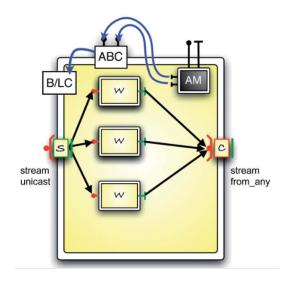

|    | 11.1  | RISC-p   | b <sup>2</sup> l                                           | 213 |

|    |       | 11.1.1   | Wrappers                                                   | 214 |

|    |       | 11.1.2   | Functionals                                                | 215 |

|    |       | 11.1.3   | Combinators                                                | 217 |

|    |       | 11.1.4   | Legal compositions of $RISC-pb^2I$ components              | 218 |

|    | 11.2  | Implen   | nenting classical skeletons/parallel design patterns       | 219 |

|    |       | 11.2.1   | Farm                                                       | 219 |

|    |       | 11.2.2   | Map                                                        | 219 |

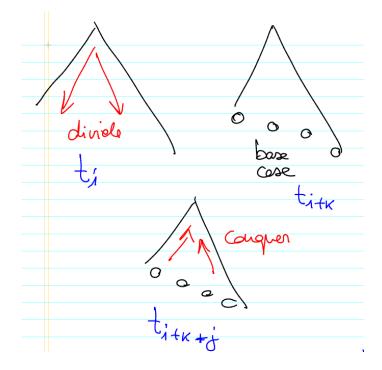

|    |       | 11.2.3   | Divide and conquer                                         | 219 |

|      | 11.3  | RISC-pb <sup>2</sup> I rewriting rules            | 220        |

|------|-------|---------------------------------------------------|------------|

|      | 11.4  | Implementing $RISC-pb^2I$                         | 221        |

|      |       | 11.4.1 Avoid introducing unnecessary overheads    | 221        |

|      |       | 11.4.2 Optimizing notable compositions            | 222        |

|      |       | 11.4.3 Implementing $RISC-pb^2I$ with FastFlow    | 224        |

| 12   | Skele | eton semantics                                    | 227        |

|      | 12.1  | Formal definition of the skeleton framework       | 227        |

|      | 12.2  | Operational semantics                             | 228        |

|      | 12.3  | Parallelism and labels                            | 232        |

|      | 12.4  | How to use the labeled transition system          | 233        |

| 13   | Surve | ey of existing skeleton frameworks                | 235        |

|      | 13.1  | Classification                                    | 235        |

|      |       | 13.1.1 Abstract programming model features        | 235        |

|      |       | 13.1.2 Implementation related features            | 236        |

|      |       | 13.1.3 Architecture targeting features            | 237        |

|      | 13.2  | C/C++ based frameworks                            | 237        |

|      |       | 13.2.1 P3L                                        | 237        |

|      |       | 13.2.2 Muesli                                     | 238        |

|      |       | 13.2.3 SkeTo                                      | 238        |

|      |       | 13.2.4 FastFlow                                   | 239        |

|      |       | 13.2.5 SkePu                                      | 240        |

|      | 10.0  | 13.2.6 ASSIST                                     | 240        |

|      | 13.3  | Java based frameworks                             | 241        |

|      |       | 13.3.1 Lithium/Muskel                             | 241        |

|      |       | 13.3.2 Calcium<br>13.3.3 Skandium                 | 241 $242$  |

|      | 13.4  | 13.3.3 Skandium<br>ML based frameworks            | 242<br>242 |

|      | 13.4  | 13.4.1 Skipper                                    | 242<br>242 |

|      |       | 13.4.2 OcamlP3L                                   | 242        |

|      | 13.5  | Other functional frameworks                       | 243        |

|      | 1010  | 13.5.1 skel (Erlang)                              | 243        |

|      | 13.6  | Component based frameworks                        | 244        |

|      |       | 13.6.1 GCM Behavioural skeletons                  | 244        |

|      |       | 13.6.2 LIBERO                                     | 245        |

|      | 13.7  | Quasi-skeleton frameworks                         | 245        |

|      |       | 13.7.1 TBB                                        | 245        |

|      |       | 13.7.2 TPL                                        | 246        |

|      |       | 13.7.3 OpenMP                                     | 246        |

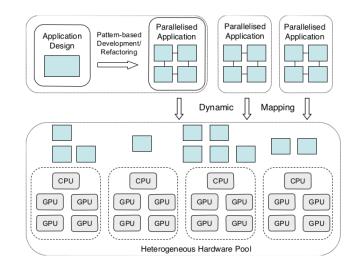

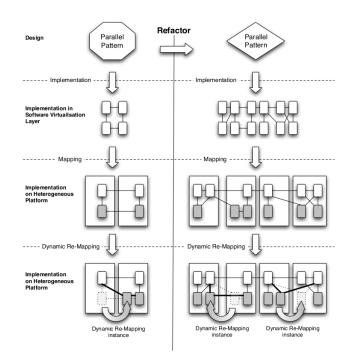

| Appe |       | A: Structured parallel programming in EU projects | 247        |

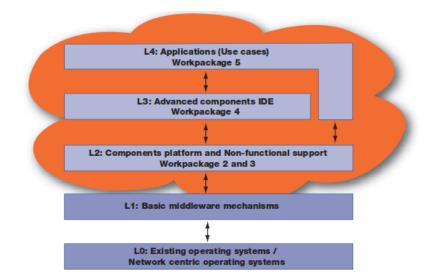

|      | A.1   | CoreGRID                                          | 248        |

|      | A.2   | GridCOMP                                          | 250        |

|      | A.3   | ParaPhrase                                        | 252        |

|      | A.4   | REPARA                                            | 255        |

\_\_\_\_\_

CONTENTS

vii

#### viii contents

1

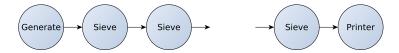

| Appendix I   | B: Fastflow                                               | 257 |

|--------------|-----------------------------------------------------------|-----|

| B.1          | Design principles                                         | 257 |

| B.2          | Installation                                              | 260 |

| B.3          | Tutorial                                                  | 260 |

|              | B.3.1 Generating a stream                                 | 264 |

| B.4          | More on ff_node                                           | 266 |

| B.5          | Managing access to shared objects                         | 269 |

| B.6          | More skeletons: the FastFlow farm                         | 273 |

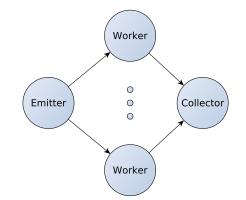

|              | B.6.1 Farm with emitter and collector                     | 274 |

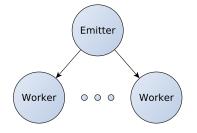

|              | B.6.2 Farm with no collector                              | 276 |

|              | B.6.3 Specializing the scheduling strategy in a farm      | 278 |

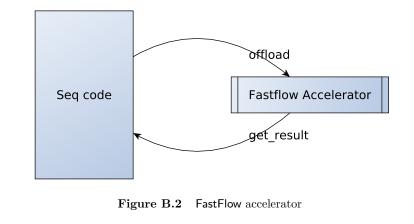

| B.7          | FastFlow as a software accelerator                        | 283 |

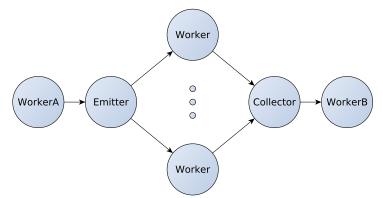

| B.8          | Skeleton nesting                                          | 287 |

| B.9          | Feedback channels                                         | 288 |

| B.10         | Introducing new skeletons                                 | 289 |

|              | B.10.1 Implementing a Map skeleton with a Farm "template" | 290 |

| B.11         | Performance                                               | 294 |

| B.12         | Run time routines                                         | 294 |

| List of Figu |                                                           | 297 |

| List of Tab  | es                                                        | 301 |

| Acronyms     |                                                           | 303 |

| Index        |                                                           | 305 |

| References   |                                                           | 309 |

## PREFACE

This material covers most of the arguments presented in the course of "Distributed systems: paradigms and models" given at the "Laurea Magistrale" in Computer Science and Networking (joint initiative by the University of Pisa and Scuola Superiore St. Anna) during the Academic year in 2012–2013. In particular, the material covers all arguments related to structured programming models and paradigms. The only arguments missing among those presented in the course are those relative to networks (wireless networks and peer-to-peer paradigm) which are covered by other, existing textbooks, as mentioned on the course web site at http://didawiki.cli.di.unipi.it/doku.php/magistraleinformaticanetworking/spm/start.

Being a kind of "working" version, you should frequently and carefully read the *errata corrige* available at the author's web site (http://www.di.unipi.it/~marcod) or on the course DidaWiki at http://didawiki.cli.di.unipi.it/doku.php/magistraleinformatican spm). Please feel free to give any suggestion or to signal any kind of error directly to author writing to the address marcod@di.unipi.it with Subject: SPM notes.

M. DANELUTTO

February 2012, Pisa, Italy

## ACKNOWLEDGMENTS

This book is the result of a long lasting activity in the field of structured parallel programming. I owe part of my experience to a number of colleagues that cooperated with me since 1990, including M. Aldinucci, F. André, B. Bacci, H. Bouziane, J. Buisson, D. Buono, S. Campa, A. Ceccolini, M. Coppola, P. D'Ambra, C. Dalmasso, P. Dazzi, D. Di Serafino, C. Dittamo, V. Getov, S. Gorlatch, L. Henrio, P. Kilpatrick, S. Lametti, M. Leyton, K. Matsuzaki, C. Migliore, S. Orlando, C. Pantaleo, F. Pasqualetti, S. Pelagatti, C. Perez, P. Pesciullesi, T. Priol, A. Rampini, D. Ratti, R. Ravazzolo, J. Serót, M. Stigliani, D. Talia, P. Teti, N. Tonellotto, M. Torquati, M. Vanneschi, A. Zavanella, G. Zoppi.

marcod

## PARALLEL HARDWARE (NEEDS PARALLEL SOFTWARE)

In recent years, a substantial improvement in computer and networking technology made available parallel and distributed architectures with an unprecedented power. The hardware revolution not only affected large parallel/distributed systems (e.g. those hosting thousands to millions of CPUs/cores in large "data center-like" installations) but also personal computing facilities (e.g. PCs, laptops and small clusters). This is mainly due to the shift from single core to multi core design of mainstream chipsets. The change from single core to multi core systems impacted also the programming model scenario. It introduced the need of (and the urgency for) efficient, expressive and reliable parallel/distributed programming paradigms and models.

In this chapter, we first outline the advances in computer architecture that took place in the last years and that are still taking place while we write these notes. Then we briefly point out the urgencies arising from these advances related to the programming model in the perspective of providing programmers with frameworks that simplify the task of developing efficient, reliable and maintainable applications for typical parallel and distributed architectures.

It is worth pointing out that within the whole book, we'll consider "parallel" and "distributed" computing as two facets of the same problem. Despite the fact parallel computing and distributed computing communities played different roles in the past and looked like two completely separated communities, we believe that distributed computing is a kind of "coarse grain" parallel computing or, if you prefer, that parallel computing if the "fine grain" aspect of distributed computing.

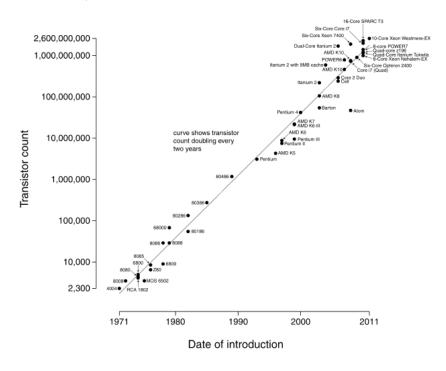

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.1 Moore's rule (Figure taken from Wikipedia)

#### 1.1 HARDWARE FOR PARALLEL/DISTRIBUTED COMPUTING

We recognize several factors that contribute to the urgency of developing efficient programming models for parallel/distributed architectures. Among those factors, we would like to mention:

- a) Evolution of CPU design and of the relative implementation techniques. When moving from single core to multi core chip design parallelism becomes the only way to exploit chip features.

- b) Evolution of high performance computer architectures, such as those appearing in the Top500 list<sup>1</sup>, that are moving more and more from dedicated architectures to tightly coupled assemblies of commodity processors through (almost) commodity interconnection network. These machines hosts hundreds of thousands of cores, and their exploitation requires correspondingly parallel/distributed applications.

- c) The advent of cloud architecture and systems. These systems host a large number of processing elements/cores and provide the users the possibility to "buy" or "rent" a partition of the cloud to be used to run their own applications. Clouds require efficient programming models paired with efficient management of the resources used, which again is a typical problem related to parallel/distributed architecture targeting.

We discuss these three aspect in more detail in the following sections.

<sup>1</sup>http://www.top500.org

The Von Neumann architecture is the one with one (or more) processing unit and a single (data and code) memory unit. Program is stored in memory and a register in the processing unit denotes the address of the next instruction to execute. It is named after the computer scientist John von Neumann (1903–1957). The interconnection between processing unit and memory is called Von Neumann bottleneck.

Figure 1.2 Von Neumann Architecture

#### 1.1.1 Evolution of CPUs

Since '60, Moore law dominated the CPU design and implementation scenario. Moore's original statement dates back to 1965. In his publication "Cramming more components onto integrated circuits", on the Electronics Magazine, he said that:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer.

As a matter of fact, in the past 40 year, the amount of components successfully placed on a single chip doubled approximately every two year.

The larger and larger number of components available on the chip have been used up to early '00 to improve the power of a single, Von Neumann style, processor, basically in two different ways:

- by increasing the word length (4 bits in 1971 to 8, 16, 32 and up to 64 bits in 2008)

- by adding more and more features that contribute to the overall CPU performance (pipelined units, super scalar design, different cache levels, out of order execution, vector/SIMD instruction set, VLIW execution units, hyper threading, virtualization support, etc.)

Along with the larger and larger number of components integrated onto the same chip, clock frequencies have been raised. This allowed to implement CPUs with shorter and shorter clock cycles. The consequences of this 40 year trend have been twofold.

On the one hand, the classical (imperative or object oriented) programming model was supported by all these CPUs and therefore old programs run on all these new CPUs. In some cases, re compilation of the source code is the only action required to port the code. In case the new architecture is from the same manufacturer, binary portability of object code is in general guaranteed<sup>2</sup> and even compilation therefore is not necessary.

On the other hand, the existing programs may be run faster and faster on the new architectures, due to the higher clock frequency and to the new features introduced in processor micro architecture.

This long running process stopped in early '00, however. Power dissipation related to the higher number of components packaged on the chip and to the higher frequencies used come to a point where chips required complex, highly efficient heat dissipation systems, possibly liquid based. The amount of power dissipated by a chip was higher that several hundred of

$<sup>^{2}</sup>$ Old instruction set are provided on the new architectures. Pentium processors can still run code compiled for 8086 in the '80 at the beginning of '00.

4 PARALLEL HARDWARE(NEEDS PARALLEL SOFTWARE)

## 1 / 1 / 1 1.4 / 2 / 2 2 / 2 / 2 (Performance / Power / Size)

Figure 1.3 Pollack's rule

Watts. In the meanwhile, the new features added to CPUs required a substantial amount of the overall chip area but provided quite limited improvements in performance.

As observed by Fred Pollack, an Intel engineer:

performance increases roughly proportional to the square root of the increase in complexity.

whereas is is known that power consumption is roughly proportional to complexity of the chip (and therefore to its area). This means that doubling the complexity of a chip only leads to a 1.4 increase in performance. However, if we use the double area to implement two smaller processors (half size of the 1.4 performance one), we get system that sports the double of performance of the original chip dissipating the double of power of the original chip.

This observation led to the development of an entirely new trend: engineers started designing more CPUs on the same chip, rather than a single, more complex CPU. The CPUs on the same chip are named *cores* and the design of the overall chip is called *multi core*.

As the chip implementation technology keeps improving with rates similar to those of the Moore's law era, a new version of the Moore law has been developed, stating that

the number of cores on a chip will double approximately every two years.

Cores in multicore chips have been redesigned to get rid of those features that require a huge area to be implemented and only contribute a modest improvement in the overall CPU performance. As an example, cores in multicore chips usually do not use out-oforder instruction execution. This allows to design smaller chips, consuming less power and, mainly, being better packable in more and more dense multicore configurations.

Multicores already dominate the CPU scenario. Today it is almost impossible to buy a computer with a single core inside, but in case of "netbooks" or ultraportable devices<sup>3</sup>. Most of PCs already<sup>4</sup> sell with dual or quad cores inside, and top end machines currently use dual quad core or eight core processors.

However, multicore architectures need explicitly parallel programs to be used efficiently. Each one of the cores in the architecture must have one or more active thread/process assigned (in average) to keep the system busy and therefore to keep the system efficiency high. This radically changed the situation. Parallel programs are *needed*. There is no chance to take an old program and run it on a multicore getting a better performance, unless the original program has already been designed and implemented as a parallel program. Indeed, due to the simplification made to the cores, it could also be the case–and it is, usually–that

$<sup>^3</sup> although currently available tablets and smart phones already include chips such as the Tegra one: a dual ARM <math display="inline">+$  nVidia GPU chip

$<sup>^{4}</sup>$  these notes are being written beginning of 2011

#### HARDWARE FOR PARALLEL/DISTRIBUTED COMPUTING

| Μ           | Μ          |   |

|-------------|------------|---|

| C2 C2 C2 C2 | C2 C2      |   |

| C1 C1 C1 C1 | C1 C1 C1 C | 1 |

| P P P P     | P P P      | Ρ |

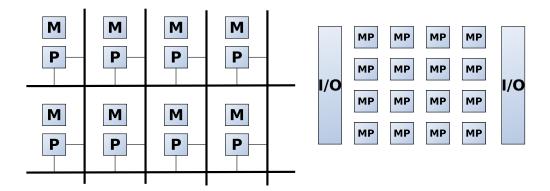

Figure 1.4 Different architectures for multicore SMP

Figure 1.5 Typical architecture of many core chips

non parallel old code runs slower on new processors. Despite the fact multicore architectures need explicitly parallel code to be exploited, their architectural design is quite traditional: a number of CPU, with private caches accessing a common shared memory space. Therefore the architectural model exposed by the micro architecture is a plain UMA SMP (Uniform Memory Access, Symmetric MultiProcessor) model (see Fig. 1.4).

However, as technology evolves, more and more cores are available on chip and many core architectures are already available today, with 64 and more cores on the same chip. These architectures include Tilera chips (up to  $100 \text{ cores}^5$ ) and the Intel experimental 80 core chip<sup>6</sup>. These CPUs make a further step in architectural design in that they release the UMA shared memory concept in favour of a regular interconnection of cores (usually based on bi-dimensional mesh topologies) with own, private memory that can be accessed routing proper messages through the on chip core interconnection network. As a consequence, the memory model becomes a NUMA model (Non Uniform Memory Access, that is accesses to different memory locations/addresses may require substantially different times) and more advanced techniques have to be used to enforce data locality and therefore achieve complete exploitation of the architecture peculiar features.

Up to now we concentrated on two CPU families: "traditional multicore" CPUs (relatively small number of cores, UMA-SMP design) and "many core" CPUs (high number of cores, NUMA memory, regular interconnection structure). There is a third kind of architectures that are being developed and used currently, namely the GP-GPU ones (General Purpose Graphic Processing Units). These architectures actually provide a huge number of cores (in the range 10-100, currently) but these cores are arranged in such a way they can

<sup>&</sup>lt;sup>5</sup>http://www.tilera.com/products/processors.php

<sup>&</sup>lt;sup>6</sup>http://techresearch.intel.com/articles/Tera-Scale/1449.htm

#### **6** PARALLEL HARDWARE(NEEDS PARALLEL SOFTWARE)

| Rank | Site                                                                  | System                                                                                                                   | Cores  | Rmax<br>(TFlop/s) | Rpeak<br>(TFlop/s) | Power<br>(Kw) |

|------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|-------------------|--------------------|---------------|

| 1    | RIKEN Advanced Institute for<br>Computational Science (AICS)<br>Japan | K computer, SPARC64 VIIIfx 2.0GHz,<br>Tofu interconnect<br>Fujitsu                                                       | 705024 | 10510.0           | 11280.4            | 12659.9       |

| 2    | National Supercomputing Center in<br>Tianjin<br>China                 | Tianhe-1A - NUDT YH MPP, Xeon X5670<br>6C 2.93 GHz, NVIDIA 2050<br>NUDT                                                  | 186368 | 2566.0            | 4701.0             | 4040          |

| 3    | DOE/SC/Oak Ridge National Laboratory<br>United States                 | Jaguar - Cray XT5-HE Opteron 6-core 2.6<br>GHz<br>Cray Inc.                                                              | 224162 | 1759.0            | 2331.0             | 6950          |

| 4    | National Supercomputing Centre in<br>Shenzhen (NSCS)<br>China         | Nebulae - Dawning TC3600 Blade<br>System, Xeon X5650 6C 2.66GHz,<br>Infiniband QDR, NVIDIA 2050<br>Dawning               | 120640 | 1271.0            | 2984.3             | 2580          |

| 5    | GSIC Center, Tokyo Institute of<br>Technology<br>Japan                | TSUBAME 2.0 - HP ProLiant SL390s G7<br>Xeon 6C X5670, Nvidia GPU,<br>Linux/Windows<br>NEC/HP                             | 73278  | 1192.0            | 2287.6             | 1398.6        |

| 6    | DOE/NNSA/LANL/SNL<br>United States                                    | Cielo - Cray XE6, Opteron 6136 8C<br>2.40GHz, Custom<br>Cray Inc.                                                        | 142272 | 1110.0            | 1365.8             | 3980          |

| 7    | NASA/Ames Research Center/NAS<br>United States                        | Pleiades - SGI Altix ICE 8200EX/8400EX,<br>Xeon HT QC 3.0/Xeon 5570/5670 2.93<br>Ghz, Infiniband<br>SGI                  | 111104 | 1088.0            | 1315.3             | 4102          |

| 8    | DOE/SC/LBNL/NERSC<br>United States                                    | Hopper - Cray XE6, Opteron 6172 12C<br>2.10GHz, Custom<br>Cray Inc.                                                      | 153408 | 1054.0            | 1288.6             | 2910          |

| 9    | Commissariat a l'Energie Atomique<br>(CEA)<br>France                  | Tera-100 - Bull bullx super-node<br>S6010/S6030<br>Bull SA                                                               | 138368 | 1050.0            | 1254.5             | 4590          |

| 10   | DOE/NNSA/LANL<br>United States                                        | Roadrunner - BladeCenter QS22/LS21<br>Cluster, PowerXCell 8i 3.2 Ghz / Opteron<br>DC 1.8 GHz, Voltaire Infiniband<br>IBM | 122400 | 1042.0            | 1375.8             | 2345          |

Figure 1.6 Top ten positions in the Top500 list, Feb 2012

only executed SIMD code (Single Instruction Multiple Data), in particular multi threaded code with threads operating on different data with the same code<sup>7</sup>.

GP-GPUs are normally used as CPU co-processors. In case data parallel code has to be executed suitable to fit the GP-GPU execution model, the code and the relative data is offloaded from main (CPU) core to the GP-GPUs cores (and private, fast memory). Then some specialized GP-GPU code (usually called *kernel*) is used to compute the result exploiting GP-GPU data parallelism and eventually results are re-read back in the CPU main memory. Overall, GP-GPU exploitation requires a notable programming effort. Open programming models have been developed to operate on GP-GPUs, such as OpenCL<sup>8</sup> and GP-GPUs manufacturers provide they own programming frameworks to access GP-GPU functionalities (e.g. CUDA by nVidia<sup>9</sup>). However, these programming frameworks require a deep knowledge of target GPU architecture and programmers have to explicitly deal with all the CPU-GPU data transfers in order to use the GPUs. This makes parallel programming of GP-GPU very expensive, at the moment being, but the fact GP-GPUs already have on board a huge number of cores (e.g. 520 cores on nVidia Fermi GPU) allows to eventually reach impressive performances in plain data parallel computations.

According to chip manufacturers, current technology allows to increase by a plain 40% *per-year* the number of on chip cores. As a result, it is expected to have an increasing number of cores per chip in the near future. With such numbers, single chip programming *must* use efficient parallel/distributed programming models, tools and implementation techniques.

<sup>8</sup>http://www.khronos.org/opencl/

$^{9} http://www.nvidia.com/object/cuda\_learn\_products.html$

<sup>&</sup>lt;sup>7</sup>At the moment being, GP-GPUs are often referred to using the term *many core* although in this book we will use the term many core to refer all those (non GPU) processors with a relatively high number of cores inside (in the range 100 to 1K)

| Processor Generation                  | Count | System Share (%) | Rmax (GFlops) | Rpeak (GFlops) | Cores   |

|---------------------------------------|-------|------------------|---------------|----------------|---------|

| Xeon 5600-series (Westmere-EP)        | 240   | 48               | 23578707.77   | 42434388.44    | 2847664 |

| Xeon 5500-series (Nehalem-EP)         | 91    | 18.2             | 7777633.81    | 11877704.02    | 1046206 |

| Opteron 6100-series "Magny-Cours"     | 34    | 6.8              | 6671696.8     | 9031446.6      | 980032  |

| Xeon 5400-series "Harpertown"         | 26    | 5.2              | 3354399.4     | 4535729.23     | 395301  |

| Opteron Quad Core                     | 17    | 3.4              | 2100788.1     | 2794468        | 307530  |

| POWER6                                | 15    | 3                | 1128793.8     | 1480537.6      | 78752   |

| POWER7                                | 14    | 2.8              | 1678583       | 2233860.45     | 73808   |

| Intel Xeon E5                         | 10    | 2                | 2769524       | 3420620.8      | 162656  |

| PowerPC 450                           | 7     | 1.4              | 2176911       | 2618162.4      | 770048  |

| Opteron 6200 Series "Interlagos"      | 7     | 1.4              | 2625043       | 3462200.2      | 363656  |

| Power BQC                             | 5     | 1                | 1427273       | 1782579.4      | 139264  |

| Itanium 2 Montecito                   | 4     | 0.8              | 227368        | 267980.4       | 42736   |

| PowerPC 440                           | 4     | 0.8              | 724683        | 906035.2       | 323584  |

| Opteron Six Core                      | 3     | 0.6              | 2731150       | 3586944        | 345602  |

| Xeon 5200-series "Wolfdale-DP"        | 3     | 0.6              | 180579        | 230169.6       | 17280   |

| Xeon 5500-series (Nehalem-EX)         | 3     | 0.6              | 1224940       | 1463569        | 161408  |

| Xeon 5300-series "Clovertown"         | 3     | 0.6              | 334480        | 434227.2       | 38320   |

| PowerXCell 8i                         | 2     | 0.4              | 1168500       | 1537632        | 136800  |

| Opteron Dual Core                     | 2     | 0.4              | 265960        | 370024.4       | 48008   |

| Xeon E7-x8xx-series (Westmere-<br>EX) | 2     | 0.4              | 129720        | 165888         | 17280   |

| SPARC64 VIIIfx                        | 1     | 0.2              | 10510000      | 11280384       | 705024  |

| NEC                                   | 1     | 0.2              | 122400        | 131072         | 1280    |

| SPARC64 VII                           | 1     | 0.2              | 110600        | 121282         | 12032   |

| PowerPC 970                           | 1     | 0.2              | 63830         | 94208          | 10240   |

| ShenWei                               | 1     | 0.2              | 795900        | 1070160        | 137200  |

| POWER5                                | 1     | 0.2              | 75760         | 92781          | 12208   |

| Core i5                               | 1     | 0.2              | 61410         | 138930         | 9900    |

| Xeon EM64T                            | 1     | 0.2              | 53000         | 64972.8        | 9024    |

#### Number of Processors share for 11/2010

In addition to the table below, you can view the visual charts using the TOP500 charts page. A direct link to the charts is also available.

| Totals                  | 500   | 100%       | 43673092.54      | 64655310.70       | 6472327          |

|-------------------------|-------|------------|------------------|-------------------|------------------|

| 128k-                   | 9     | 1.80 %     | 8681851          | 12409784          | 1666146          |

| 64k-128k                | 5     | 1.00 %     | 4655000          | 6694211           | 483678           |

| 32k-64k                 | 17    | 3.40 %     | 5227787          | 8820874           | 783950           |

| 16k-32k                 | 20    | 4.00 %     | 3375425          | 4351903           | 506760           |

| 8k-16k                  | 96    | 19.20<br>% | 7607941          | 10538478          | 1037103          |

| 4k-8k                   | 291   | 58.20<br>% | 11685027         | 18923817          | 1769924          |

| 2049-4096               | 60    | 12.00<br>% | 2284042          | 2716312           | 221438           |

| 1025-2048               | 2     | 0.40 %     | 156020           | 199932            | 3328             |

| Number of<br>Processors | Count | Share<br>% | Rmax Sum<br>(GF) | Rpeak Sum<br>(GF) | Processor<br>Sum |

Figure 1.7 Sample summary figures relative to Top500 Nov. 2011 (top) and Nov. 2010 list (bottom)

1

#### 8 PARALLEL HARDWARE(NEEDS PARALLEL SOFTWARE)

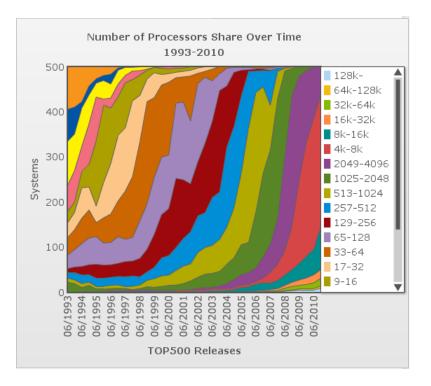

Figure 1.8 Historic/trend charts relative to Top500 (sample)

#### 1.1.2 High performance computing architectures

Traditionally, we label as "high performance computing" all those activities involving a huge amount of computation/data. High performance computers are therefore those big "machines" usually owned by big institutions or departments, able to perform impressive amount of computations per unit of time and build out of an actually huge number of processing elements.

Since year, the www.top500.org web site maintains a classification of the world most powerful single computer installations. A list is published twice per year, in June and November, hosting the top 500 computer installations in the world. The installation are ranked by running a standard benchmark suite. Fig. 1.6 shows the top ten positions of the list published in Nov 2010. Data relative to any one of the lists published from 1993 on may be "summarized" also according to different parameters such as the number of processors/cores in the system, the kind of processors or interconnection network, the operating system used, etc. A sample of these summary tables is shown in Fig. 1.7.

But the more interesting possibility offered by the Top500 lists is the possibility to see the evolution of the features of the Top500 installations in time. Fig. 1.8 shows<sup>10</sup> one of the charts we can get summarizing the evolution in time of one of the features of the Top500 computers, namely the number of processors/cores included.

Looking at these time charts, several trends may be recognized in these high end systems:

• the number of processing elements is constantly increasing. Recently the increase in processor count has been partially substituted by the increase in core per processor count.

<sup>10</sup>the graph is in colors, there is no way to get it in black&white. Therefore it may be hardly read on printed version of the book. However, it can be easily regenerate "on screen" pointing a browser to the http://www.top500.org/overtime/list/36/procclass web site.

- most of the systems use scalar processors, that is "vector" processors–quite popular for a period in this kind of systems–constitute a less and less significant percentage of the totals.

- GP-GPUs are pervading the Top500 systems. More and more systems hosts nodes with GP-GPU coprocessor facilities. This makes the systems heterogeneous, of course.

- interconnection networks are evolving from proprietary, special purpose networks to optimized versions of a limited number of networks (Ethernet and Infinibad)

- Linux jeopardized all the other operating systems and currently runs more that 90% of the total of the systems

- these systems are used to run a variety of applications. The most popular one are financial applications (about 8.6% in Nov. 2010 list), research applications (about 16.4%) and "not specified" applications (about 34%) which unfortunately also include military applications.

From these trends we can therefore conclude that:

- we need programming environments able to efficiently manage more and more processing elements. The Top500 applications are mostly written using low level, classical programming environments such as MPI or OpenMP.

- we need programming environments able to efficiently manage heterogeneous architectures, such as those with GP-GPU equipped processing elements.

- we need programming environments supporting functional and performance portability across different parallel architectures, to be able to move applications across Top500 systems.

#### 1.1.3 Cloud

The term *cloud computing* has been introduced in the '2000s and refers to the provisioning of computer resources to run some kind of application that may be sequential or parallel. The idea of *cloud* recalls the idea of a pool of resources with some kind of "undefined borders". The cloud resources are made available "on request" to the final user, that usually pays the access to the cloud per resource and per time used.

Clouds have been invented by industry/commercial companies, in fact. On the one side, several companies were using for their own purposes a huge number of workstations connected through some kind of private network. These collections were often dimensioned on peak necessities and therefore part of the resources were unused for a consisted percentage of time. Therefore these companies thought it was convenient to find ways of selling the extra power of this computing element agglomerate in such a way the investment made to set up the collections of computing elements could be more fruitful. On the other side, other companies found convenient to invest in computing resources and to sell the *usage* of these computing resources to persons/companies that could not afford the expense to buy, run and maintain the hardware resources they occasionally or permanently need but can anyway use some budget to use the resources from a provider.

As a matter of fact, in less than 10 years a number of companies are providing cloud services (including Amazon, Microsoft, Google) and the model is also currently being exported as a convenient way to organize companies internal services.

At the moment being, an assessed "cloud" concept can be summarized as follows:

cloud computing is a computing model that guarantees on-demand access to a shared pool of computing resources. The computing resources may include processing nodes, **10** PARALLEL HARDWARE(NEEDS PARALLEL SOFTWARE)

interconnection networks, data storage, applications, services, etc. and they can be configured to accomplish user needs with minimal management effort through a well defined interface.

where the key points are

- **Computing model** This provides a computing model. The user must adopt this exact computing model to be able to use cloud computing.

- **On-demand** Resources in the cloud are provided on-demand. There is no "reserved" resource in the cloud: cloud applications express their needs through suitable APIs and the cloud management software allocated the needed resources when the application is run. This, in turn, means that the user application may no rely on any physical property of the resources used. Different runs may get different physical resources. Therefore everything (hw) is accessed through proper virtualization services.

- **Shared** The resources in the pool are shared among cloud users. Cloud management software will ensure separation among the logical resources accessed by different users.

- **Different resources** The resources accessed through the cloud may be processing, storage or interconnection resources—on the hardware side—as well as application or service resources—on the software side.

- **Configurable** Some configuration activity is requested to be able to access cloud resources. The configuration usually consists in writing some XML code specifying the "kind" of resources needed. In some other cases it may also consist in more specific programming activity interacting with the cloud APIs.

- This definition of cloud is usually interpreted in three slightly different ways:

- **SaaS** At the application level, clouds may be perceived as a set of services that can be accessed to compute results. We speak of *Software As A Service* (SaaS) in this case.

- **PaaS** At the hardware level, clouds may be perceived as platforms of interconnected processing elements that execute user applications. In this case we speak of *Platform As A Service* (PaaS).

- **IaaS** At an higher level with respect to PaaS we can perceive cloud as a virtual infrastructure, that is a hardware/software virtual environment used to run user applications. User applications in this case are rooted in the software tools provided by the infrastructure rather than directly on the virtualized hardware as it happened in the PaaS case. In this case we speak of *Infrastructure As A Service* (IaaS).

- E.G.▷ As an example, if we develop a cloud application that uses the services provided by the cloud to reserve flight seats or hotel rooms to provide the final user the possibility to organize a trip to given place for a given amount of days, we are using a SaaS. If we prepare a cloud application were a number of virtual machines running our own customized version of Linux to run an MPI application on top of them, we are using a PaaS. Eventually, if we write a cloud MPI application we are using IaaS, as in this case the cloud will provide us the operating system + MPI virtual abstraction.

When using cloud for parallel computing care has to be taken to make an efficient usage of the resources claimed. The kind of actions taken also depends on the kind of usage (SaaS, PaaS or IaaS) we make of the cloud. Let us restrict to a PaaS usage. If we prepare our set of virtual machines to be eventually run on the cloud resources we have to be aware that both different virtual machines may be allocated to different hardware resources and that different runs of our application may eventually get assigned different resources. Therefore, we must carefully access "system" resources through virtualization interfaces. Interconnection network should be accessed through is POSIX/TCP interface exposed by the PaaS, or the processing elements must be accessed to their generic specifications exposed (e.g. Intel IA32 architecture), for instance.

Due to this variance in the assigned resources some dynamic adaptation should be probably included in the application non functional code, to achieve the best efficiency in the usage of the "unknown" resources eventually assigned.

#### 1.2 PARALLEL SOFTWARE URGENCIES

By looking at the three different aspects outlined in the previous Section, we can try to list a set of different urgencies (along with the connected *desiderata*) relative to the parallel programming environments. In this Section we briefly discuss the main items in this list.

*Parallelism is everywhere.* Parallelism is moving from HPC systems to all day systems. Personal computers, laptops and, recently, tablets and smart phones, have multi core processors inside. The amount of cores per processor is increasing constantly with time. We should expect to have a significant numbers of cores in any of these personal system within a few years. We therefore need to develop parallel computing theory, practice and methodologies rather than further developing sequential only their sequential counterparts. In particular, future programmers should be formed with parallelism in mind: we must abandon the idea that sequential algorithms come first and then they can be parallelized. These new programmers must start thinking to the problems directly in a parallel computing perspective.

Heterogeneous architectures are becoming important. With the advent of GP-GPUs most processing elements will have some kind of co-processor in the near future. GP-GPUs sport an impressive number of cores that unfortunately may be used only for particular kind of parallel computations, namely data parallel style computations. Parallel programming frameworks should be able to seamlessly support these heterogeneous architectures and should provide the application user with high level tools to access co-processor resources. This is even more important taking into account that heterogeneous architectures with FPGA based co-processors start to be available<sup>11</sup>. FPGAs are particular circuits that may be configure to perform different computations directly "in hardware". Being completely configurable they offer huge possibilities to improve critical portions of applications by directly programming "in hardware" these portions of code. However, this is a quite complex task definitely outside the possibilities of the application programmers. Programming frameworks should be able to provide high level access API also for this kind of accelerators. Outside the single processor features, even if we consider "distributed" architectures such as  $COW/NOW^{12}$  architectures we have to take into account that rarely the systems hosted are identical. Some of them may be equipped with co-processors. More in general, upgrade due to normal system maintenance will introduce some degree of heterogeneity in the system.

$<sup>^{11}</sup>see \ Intel \ Atom \ E6x5C \ series \ http://edc.intel.com/Platforms/Atom-E6x5C/ \ http://newsroom.intel.com/community/intel_newsroom/blog/tags/system-on-chip$

$<sup>^{12}\</sup>mathrm{COW}$  is the acronym of Cluster Of Work stations, whereas NOW is the acronym of Network Of Work stations

#### 12 PARALLEL HARDWARE(NEEDS PARALLEL SOFTWARE)

Parallel program portability is an issue. Parallel program portability is an issue, especially if non functional feature portability is considered in addition to functional portability<sup>13</sup>. Functional portability is usually ensured by the software platform targeted. An MPI program running on the first computer in the Top500 list may be quite easily ported on a different computer of the same list as well as on your own laptop. Of course the performances achieved and the amount of data processed will be affected. First of all, different amounts of memory may accommodate the execution of programs using differently sized input/output data. This is normal and it also happens in the sequential scenario. However, even in case the same data sizes may be processed different configuration in terms of the interconnection network and of the kind of processing elements used may lead to very different performance results for the very same parallel application. A decent parallel programming framework should ensure performance portability across different target architectures as much as possible, modulo the fact that nothing can be done in case of "insufficient" resources. Performance portability is not the only one non functional concern portability issue, however. Nowadays power management policies represent a significant non functional concern and again we wish to have parallel programming frameworks capable to support power management policy portability across different target architectures<sup>14</sup>.

*Code reuse is an issue.* When developing a parallel application we will often be in the situation that a huge amount of sequential code already exists solving (part of) the different problems that have to solved in our application. These sequential codes are often the result of years of development, debugging and fine tuning. Rewriting them is therefore simply an unfeasible hypothesis. Any parallel programming framework must therefore support re-use of existing code as much as possible. In turn, this means that it must provide the possibility to link this code in those parts of the parallel application solving the particular problem solved by the sequential code and to orchestrate parallel execution of different instances of these sequential codes as well.

Dynamic adaptation must support non exclusive usage of parallel resources. When writing parallel code for cloud systems, as well as for architectures not in exclusive access, we must take into account of the varying features of the hardware used. Parallel software frameworks must provide support for the development of dynamic adaptation policies to get rid of the inefficiencies introduced by the varying features of the target architecture. The support must be efficient enough to support reconfiguration of the running application with a minimal overhead.

<sup>13</sup>see Sec. 2.3 for the definition of functional/non functional properties in a parallel computation  $^{14}$ e.g. we want programming environments capable to guarantee that a "power optimal" implementation of an application on target architecture A may be ported to architecture B preserving power optimality, either by simple recompilation or by some kind of automatic application restructuring

#### A generally assessed definition of parallel computing can be stated as follows: Parallel computing is the use of two or more processing elements in combination to solve a single problem.

At the very beginning of the parallel computing story "processing elements" where actually full computers, while nowadays they can be full computers as well as cores in general purpose (CPU) or special purpose (GPU) units. Also the term "two or more" was really referring to numbers in the range of ten, while nowadays it may range up to hundreds of thousands<sup>15</sup>.

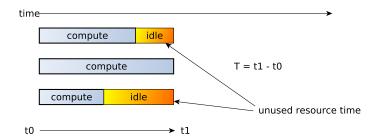

Despite the different types and number of processing elements used, however, parallel computing is a complex activity requiring different steps to produce a running parallel program:

- First, the set of possibly *concurrent activities* have to be identified. Concurrent activities are those activities that may be performed in concurrently/in parallel. Activities that may be performed concurrently exclusively depend on the features of the problem we want to solve. When defining the set of concurrent activities we defined both *which* and *how many* concurrent activities we have.

- Then, proper *coordination* of the concurrent activities has to be designed. Coordination includes synchronization as well as access to logically shared data from within different concurrent activities identified in the first step. Coordination features are derived from the features of the problem to solve and from the features of the set of concurrent activities devised in the first step.

- Last but not least, the concurrent activities and the related coordination activities *must be implemented*—in parallel—with the tools available and trying to maximize the

$^{15}{\rm The}$  "supercomputer" currently in the top position of the www.top500.org list sports 186368 cores (Nov. 2010 list)

SPM notes 2012–2013. By M. Danelutto DRAFT – version 1.1 – February 2012

benefits of parallel execution. As an example, trying to minimize the wall clock time spent to solve the problem at hand. While implementing the concurrent activities with the available tools we can eventually realize that some of the logically concurrent activities are not worth begin parallelized as no benefits derived from their implementation "in parallel". Possibly, the tools available to support parallel implementation of concurrent activities will be such that the concurrent activities individuated in the first step may not be used to produce any kind of improvement–in terms of performance–of the application, and therefore we have to go back to step one and look for an alternative decomposition of our problem in terms of concurrent activities. In any case, the implementation of concurrent activities in parallel performed in this last step *depends on the tools and on the features of the parallel architecture we are targeting.*

E.G.⊳ As an example, let us suppose we want to implement a parallel application transforming a color image in a black&white image. Conceptually, the image is an array of pixels. Each pixel is defined by a color. The set of concurrent activities we can individuate is such that we have one concurrent activity for each one of the pixels of the image. Each one of these activities will simply transform pixel representation according to a function  $f : RGB \to B\&W^{16}$  mapping color pixels to black and white pixels. After having individuated the possibly concurrent activities needed to solve our problem, we investigate the kind of coordination needed among these activities. In our case, all the individuated concurrent activities may actually start in concurrently, provided concurrent accesses are supported to the different image pixels. Then we have to wait for the termination of all the concurrent activities in order to establish that our computation is completed, that is that our problem has been solved.

Let us consider we are using a shared memory multi core architecture with 16 cores to implement our application, and that the image to transform has been already allocated in memory. We can therefore implement each pixel transformation concurrent activity as a separate thread. We can start all the threads (one per pixel) in a loop and then wait for the termination of all those threads. The possibility to access single pixels of the image concurrently–for reading the color value and for writing the computed grey value–is guaranteed by the global shared memory abstraction exposed by threads.

We can easily recognize that the loop starting the threads and the one waiting for thread completion are huge, due to the huge numbers of pixels in the image, with respect to the number of cores in the target machine, which in turn determines the actual maximum parallelism degree of our application. Therefore we can "restrict" the number of parallel activities originally found in our problem by programming the application in such a way the image pixels are partitioned in a number of sub-images equal to the number of cores in our target architecture. The structure of the final parallel application remains the same, only the parallelism degree changes to match the parallelism degree of the architecture. This will obviously be a much better parallel implementation than the first one: no useless–i.e. not corresponding to the actual parallelism degree of the target architecture–parallelization has been introduced in the code.

What if the target architecture was a network of workstations instead? we should have used processes instead of threads and we should also have programmed some specific communication code to send the parts of the images to be processed to the different processes used. Due to longer time required both to start a process on a remote machine (w.r.t. the time needed to start a thread on a multicore) and to communicate over interconnection network (w.r.t. the time spent to implement an independent–e.g. not synchronized–access to the image pixels in main memory) this obviously requires a careful design of the implementation grouping large number of potentially concurrent activities into a much smaller number of processes to be run on different processing elements in the network.

<sup>&</sup>lt;sup>16</sup>we denote with  $f : \alpha \to \beta$  a function mapping values of type  $\alpha$  to values of type  $\beta$ , as usual in functional style

Looking in more detail at the three steps detailed above, we can refine the different concepts just exposed.

*Concurrent activities.* When determining which are the possibly concurrent activities that can be used to solve our problem, we determine the candidates to be implemented in parallel. Two kind of approaches may be followed:

- we may look for *all* the concurrent activities we can figure out and assume that implementation will extract from the whole (possibly large) set those actually being worth to be implemented in parallel, that is the exact subset "maximizing" the performance of our application.

- Alternatively, we may directly look for *the best* decomposition of the problem in concurrent activities, that is the set of concurrent activities that, if implemented in parallel (all of them), lead to the better performance values in the computation of our problem.

The first approach clearly only depends on the features of the problem we want to solve, while the second one also depends on the features of the target architecture we want to use<sup>17</sup>. In general, different alternatives exists to devise the number and the kind of concurrent activities needed to solve a problem. Again, *all* possible alternatives may be devised in this phase or-more likely-one alternative is selected and other alternatives are possibly considered later on in case of negative feedbacks from the implementation phase.

*Coordination.* Coordinating concurrent activities is related to two different aspects: synchronization and data access. The synchronization aspects are related to problem of "ordering" the concurrent activities. Some activities may need results from other activities to start their computation and therefore some synchronization is needed. In other cases a set of concurrent activities must be started at a given time, for instance after the completion of another (set of) concurrent activity (activities). The data access aspects are related to the possibility for concurrent activities to access common data structures. Concurrent accesses have to be regulated to ensure correctness of the concurrent computations. Regulation of common (shared) data access depends on the kind of accesses performed. Concurrent read accesses to a read only shared data structure usually do not pose problems, while concurrent write accesses to a shared data structure must be properly scheduled and synchronized. Also, coordination may be achieved via accesses to shared data structures or via message passing. The usage of shared memory accesses and message passing can be combined to optimize coordination of concurrent activities in environments supporting both mechanisms.

*Implementation*. Implementation requires considering several problems, including parallel activities implementation, coordination implementation and resource usage. *Parallel activities* may be implemented with several different and partially equivalent mechanisms: processes, threads, kernels on a GPU, "hardware" processes, that is processes computed on specialized hardware such as programmable FPGA co-processors or specific hardware coprocessors. *Coordination* implementation may exploit different mechanisms, such as those typical of shared memory environments or of message passing environments. Very often the coordination activities must take into account the possibilities offered by interconnection networks, internal or external to the processing elements. As an example, in clusters of workstations the interconnection network may support forms of broadcasting and multicasting that greatly enhance the possibilities to implement efficient collective<sup>18</sup> coordination

<sup>&</sup>lt;sup>17</sup>target architecture in terms of both software (compilers and run times available) and hardware (number and kind of processing elements/resources available.

$<sup>^{18}\</sup>mathrm{i.e.}$  involving a set of parallel activities/actors

operations. In a multicore, the UMA or NUMA<sup>19</sup> memory hierarchy may force particular allocation of shared data in memory in order to achieve efficient parallel activities coordination. *Resource usage* concerns the allocation of parallel activities to the resources (cores, processing elements, memory locations, etc.) actually available. In turn, this means that both *mapping*-assigning parallel activities to processing resources-and *scheduling*-starting and stopping parallel activities-policies and strategies must be devised. In general most of the problems related to mapping and scheduling are NP-complete problems, and therefore in most cases proper heuristics are used instead of exact algorithms.

#### 2.1 CONCURRENT ACTIVITY GRAPH

The concurrent activities individuated in the first step performed to produce a parallel implementation of a given application is the starting point for all the implementation activities, the ones performed in the thirds step mentioned at the beginning of this Chapter. Actually, the starting point we have to consider includes both the concurrent activities and the actions needed to coordinate them in the parallel application.

We therefore introduce a formalism aimed at modeling the concurrent activities needed to implement a given parallel application: the *concurrent activity graph*. The concurrent activity graph is defined as a graph:

$$\mathcal{G} = (A, N)$$

where the nodes  $(n \in N)$  are concurrent activities and arcs represent two different types of relations among nodes, that is  $A = C_d \cup D_d$ , where :

- the control dependencies  $C_d$ , are those dependencies explicitly given by the programmer and to establish an ordering in the execution of concurrent activities.  $\langle n_1, n_2 \rangle \in C_d$  represents the fact that the activity represented by node  $n_2$  must be executed after the end of the activity represented by node  $n_1$ .

- data dependencies are those dependencies  $\langle n_1, n_2 \rangle \in D_d$  modeling the fact that a data item produced by concurrent action modeled by node  $n_1$  is needed to compute the concurrent activity modeled by node  $n_2$ .

Activities that do no have dependencies (neither control nor data dependencies) may be executed in parallel. Activities linked by a control or data dependency must be executed sequentially, although they can be executed in parallel with other concurrent activities.

Within the graph  $\mathcal{G}$  we can identify *input activities* as those activities that are activated by the presence of application input data, and *output activities* as those activities that produce the data relative to final parallel application result.

Within the graph, we also identify the *critical path*, as the "longest" path of activities connected by control or data dependencies from an input node to an output node. "Longest" in this context has to be understood in terms of performance. As suggested by the name, critical path is the natural candidate when looking for optimizations in a parallel application. In fact, as a critical path starts with the availability of the input data and application results may only be delivered when all the output activities, including the one concluding the critical path, are terminated, the best time we can achieve in the execution of our parallel application is the time taken in the execution of the whole critical path<sup>20</sup>.

<sup>&</sup>lt;sup>19</sup>(Non)Uniform Memory Access. In a UMA architecture, all accesses to main memory costs the same time independently of the position of the core requiring the access. In a NUMA architecture, different cores may take different times to access the same shared memory location. The differences in time may be considerable.

$<sup>^{20}</sup>$  i.e. of the set of concurrent activities included in the critical path

We want to point out that the graph  $\mathcal{G}$  is a logical graph, that is it corresponds to the logically concurrent activities we individuated among the overall activities to be performed in order to get the problem solutions.

Later on, we will speak of similar *implementation* graphs that refer to the parallel activities performed in the implementation of our concurrent activities graph. That graph could be sensibly different and is definitely dependent on the features of the target platform (hw and sw).

#### 2.2 COORDINATION

Once the set of possibly concurrent parallel activities has been individuated, the next step consists in designing the proper coordination of these concurrent activities. Those activities that turn out to be *completely independent*—i.e. those activities that do not have dependencies on each other—may be coordinated in a simpler way than those activities that instead depend somehow one on the other.

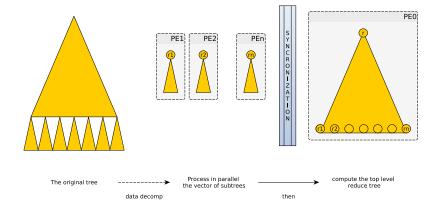

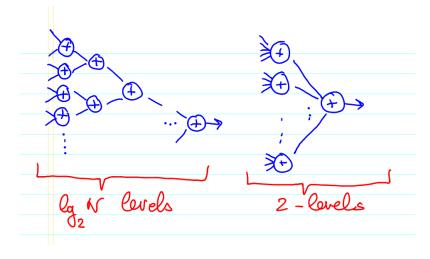

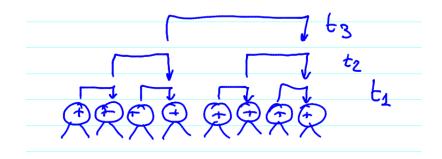

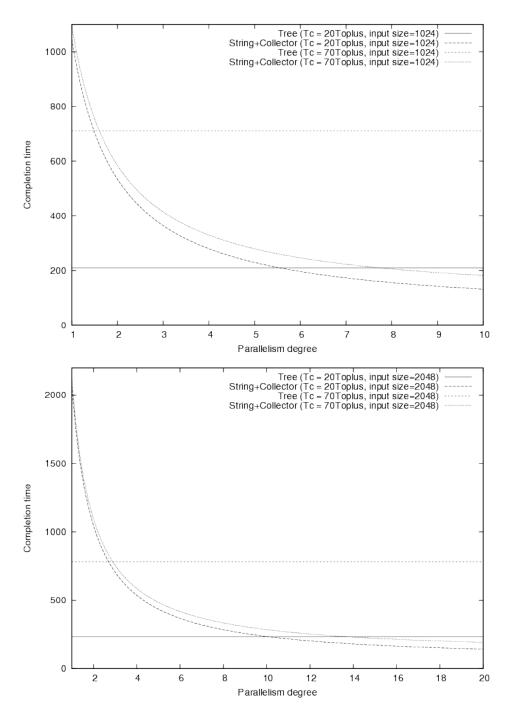

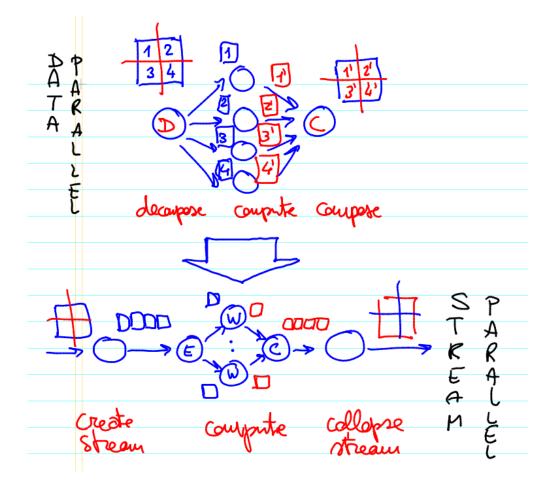

A number of different coordination mechanisms may be used to purpose: